Silkscreen-to-Pad Spacing Requirements for Component Footprints

Abstract: The relative position between silkSCReen and pads critically impacts PCBA manufacturability, inspectability, and reliability. Per IPC-7351/2221 standards, the core principle is "silkscreen must not contact pads, with sufficient clearance to prevent ink contamination." The general spacing requirement is ≥0.2mm (8mil), compressed to ≥0.1mm (4mil) for high-density designs. This article details technical specifications and failure analysis.

1. General Spacing Standards

-

Basic Clearance:

-

Standard Components: Silkscreen boundary ≥0.2mm from pad edge (IPC-7351 5.3.2), preventing solder mask ink oveRFlow during wave soldering.

-

High-Density Areas: ≥0.1mm (e.g., 0.4mm-pitch QFN), requiring laser-engraved silkscreen (±0.02mm precision).

-

-

Polarity Marking Requirements:

-

Polarity symbols ("+"/"-"/"◁") must be ≥0.25mm from pads, with character height ≥1.0mm for legibility (IPC-2221B 9.1).

-

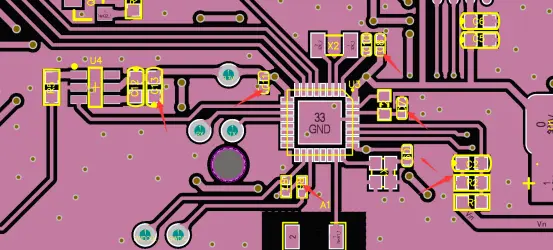

2. Spacing Requirements by Component Type

| Component | Min. Silk-Pad Spacing | Silk Line Width | Key Constraints |

|---|---|---|---|

| Chip (≥0402) | 0.15mm | 0.15mm | Silk must not cover component terminals |

| SOP/QFP | 0.20mm | 0.18mm | Pin 1 marker extends 0.3mm beyond corner |

| BGA | 0.10mm | 0.12mm | No silk projection over ball array area |

| Connectors | 0.30mm | 0.25mm | Outline must fully enclose mounting holes |

Note: Silkscreen must avoid thermal pads completely (≥0.5mm clearance) to prevent carbonization.

3. Failure Modes of Insufficient Spacing

-

Soldering Defects:

-

Silk ink contacting pads → Flux contamination → Poor wetting (↑40% cold joint rate).

-

-

Inspection Failures:

-

AOI false "missing component" calls due to silk overlapping pad edges (↑30% error rate).

-

-

Reliability Risks:

-

High-temperature ink decomposition → Organic contamination → ↑50% CAF (conductive anodic filament) risk.

-

4. Design Rules & Process Compensation

-

Footprint Library Design:

-

Pad Expansion: Set EDA clearance rules (e.g.,

silk_to_pad = 0.2mmin Cadence). -

Polarity Marking Priority: Place symbols near component body center, not between pads.

-

-

Process-Specific Adjustments:

Process Spacing Compensation Basis Screen Printing +0.05mm ±0.04mm ink diffusion from stencil distortion Laser Direct Imaging +0.02mm ±0.015mm alignment accuracy Inkjet Printing -0.03mm Controlled ±0.01mm droplet spread -

High-Density Board Optimization:

-

Micro-Silkscreen: 0.8mm character height/0.1mm line width (requires 20× magnification).

-

Critical Area Omission: Omit outlines under BGAs; retain only designators.

-

5. Verification & Inspection Methods

-

DFM Simulation:

-

Use Valor NPI or HQDFM for silkscreen conflict check (alerts if spacing <0.1mm).

-

-

First-Article Inspection:

-

3D Optical Profilometry: Measure ink thickness (standard ≤25μm; excess causes spacing failure).

-

Thermal Aging: Check for cracks/migration after 500h at 125℃.

-

-

Mass Production Control:

-

AOI with silk-pad overlap detection algorithm (sensitivity: 0.15mm; escape rate <0.5%).

-

Conclusion

Silkscreen-to-pad spacing balances manufacturability, readability, and reliability:

-

General Standard: ≥0.2mm (IPC baseline), ≥0.1mm for high-density areas.

-

Core Principles:

-

Zero silk-pad contact,

-

Unambiguous polarity/designator marking.

-

PCB

PCB FPC

FPC Rigid-Flex

Rigid-Flex FR-4

FR-4 HDI PCB

HDI PCB Rogers High-Frequency Board

Rogers High-Frequency Board PTFE Teflon High-Frequency Board

PTFE Teflon High-Frequency Board Aluminum

Aluminum Copper Core

Copper Core PCB Assembly

PCB Assembly LED light PCBA

LED light PCBA Memory PCBA

Memory PCBA Power Supply PCBA

Power Supply PCBA New Energey PCBA

New Energey PCBA Communication PCBA

Communication PCBA Industrial Control PCBA

Industrial Control PCBA Medical Equipment PCBA

Medical Equipment PCBA PCBA Testing Service

PCBA Testing Service Certification Application

Certification Application RoHS Certification Application

RoHS Certification Application REACH Certification Application

REACH Certification Application CE Certification Application

CE Certification Application FCC Certification Application

FCC Certification Application CQC Certification Application

CQC Certification Application UL Certification Application

UL Certification Application Transformers, Inductors

Transformers, Inductors High Frequency Transformers

High Frequency Transformers Low Frequency Transformers

Low Frequency Transformers High Power Transformers

High Power Transformers Conversion Transformers

Conversion Transformers Sealed Transformers

Sealed Transformers Ring Transformers

Ring Transformers Inductors

Inductors Wires,Cables Customized

Wires,Cables Customized Network Cables

Network Cables Power Cords

Power Cords Antenna Cables

Antenna Cables Coaxial Cables

Coaxial Cables Net Position Indicator

Net Position Indicator Solar AIS net position indicator

Solar AIS net position indicator Capacitors

Capacitors Connectors

Connectors Diodes

Diodes Embedded Processors & Controllers

Embedded Processors & Controllers Digital Signal Processors (DSP/DSC)

Digital Signal Processors (DSP/DSC) Microcontrollers (MCU/MPU/SOC)

Microcontrollers (MCU/MPU/SOC) Programmable Logic Device(CPLD/FPGA)

Programmable Logic Device(CPLD/FPGA) Communication Modules/IoT

Communication Modules/IoT Resistors

Resistors Through Hole Resistors

Through Hole Resistors Resistor Networks, Arrays

Resistor Networks, Arrays Potentiometers,Variable Resistors

Potentiometers,Variable Resistors Aluminum Case,Porcelain Tube Resistance

Aluminum Case,Porcelain Tube Resistance Current Sense Resistors,Shunt Resistors

Current Sense Resistors,Shunt Resistors Switches

Switches Transistors

Transistors Power Modules

Power Modules Isolated Power Modules

Isolated Power Modules DC-AC Module(Inverter)

DC-AC Module(Inverter) RF and Wireless

RF and Wireless