Layout Distance Guidelines for Decoupling Capacitors Relative to IC Power Pins

Abstract: The placement distance of decoupling Capacitors critically impacts power integrity (PI) and signal integrity (SI). For high-frequency capacitors like 0.1μF, the optimal distance to IC power pins should be 1–3mm to minimize loop inductance. This article analyzes distance constraints and optimization strategies based on IPC-2221, IEEE PDN Standards, and empirical data.

1. Core Impact of Distance on Power Integrity

-

Parasitic Inductance Effect:

-

Each 1mm increase adds ≈1nH loop inductance (Formula:

L=5×ln(D)×h, D: distance, h: layer thickness). -

Excessive inductance (>2nH) nullifies decoupling: At >100MHz, 0.1μF capacitor impedance spikes from 0.5Ω to 5Ω when distance=3mm.

-

-

Critical Distance Calculation:

-

Minimum: ≥1mm (prevents IC damage from soldering thermal shock)

-

Maximum: ≤3mm (ensures low impedance in 10–100MHz target band)

-

2. Tiered Layout Standards

| IC Type | Capacitor Distance | Quantity per Pin | Key Constraints |

|---|---|---|---|

| Low-Speed MCU (≤50MHz) | ≤5mm | 1–2/pin | Place near power plane entry |

| High-Speed CPU/FPGA | ≤1.5mm | 1/pin | Direct pin-cap-GND via connection |

| RF ICs (>1GHz) | ≤1mm | 2–4/pin (multi-value) | No crossing plane splits |

Note: For BGAs, follow the "3C Rule": Capacitor→Via→Contact path length < 2.5mm.

3. Failure Modes vs. Distance

-

Consequences of Excessive Distance (>3mm):

-

Power noise ↑300mV (vs. spec <±50mV), causing IC reset failures;

-

Signal edge ringing ↑40%, eye closure rate >30%.

-

-

Common Layout Errors:

-

Capacitor at power path end → ↓90% high-frequency noise suppression;

-

Vias between cap and pin → +0.5nH inductance per via.

-

4. Optimization Techniques

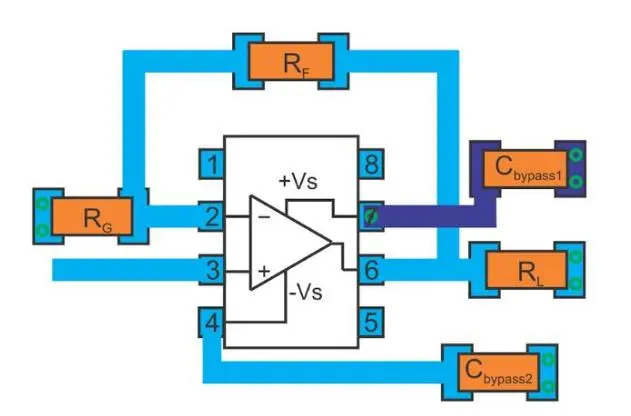

Topology Selection:

-

Star Configuration: Single capacitor for multi-pin ICs (≤1.5mm to center pin);

-

Distributed Layout: Dedicated capacitor per 1–2 power pins (for BGAs).

[IC Pin]---(≤1mm)---[Cap]---(≤0.5mm)---[GND Via] -

Via Design Rules:

-

Direct dual vias (≥0.2mm dia.) from capacitor pads to shorten current loops;

-

Via spacing ≤0.3mm reduces equivalent inductance (single via≈0.3nH, dual≈0.15nH).

-

-

Stackup Strategy:

-

Capacitors must be on the same side as IC, no cross-layer routing (+0.8nH inductance);

-

Power/GND plane spacing ≤0.2mm (4-layer stack: L2-GND, L3-PWR).

-

5. Verification & Simulation

-

PDN Impedance Simulation:

-

Target impedance:

Z_target = (V×Ripple%) / I_max(e.g., 1.8V/5% ripple/2A load → Z≤36mΩ); -

Capacitor placement must flatten impedance curve in 10–100MHz band (<±10% fluctuation).

-

-

Validation Tests:

-

VNA (Vector Network Analyzer): Measure S21 insertion loss (<-40dB@100MHz);

-

Oscilloscope with Ground Spring: Probe power noise (BW≥500MHz), Vpp<50mV.

-

Conclusion

The core principles for 0.1μF decoupling capacitor placement are "minimize distance + minimize loop inductance":

-

General Standard: 1–3mm from IC power pins; ≤1.5mm for high-speed designs.

-

Critical Measures:

-

Direct pin-to-cap connection without intermediate vias,

-

GND via ≤0.5mm from capacitor pad.

-

PCB

PCB FPC

FPC Rigid-Flex

Rigid-Flex FR-4

FR-4 HDI PCB

HDI PCB Rogers High-Frequency Board

Rogers High-Frequency Board PTFE Teflon High-Frequency Board

PTFE Teflon High-Frequency Board Aluminum

Aluminum Copper Core

Copper Core PCB Assembly

PCB Assembly LED light PCBA

LED light PCBA Memory PCBA

Memory PCBA Power Supply PCBA

Power Supply PCBA New Energey PCBA

New Energey PCBA Communication PCBA

Communication PCBA Industrial Control PCBA

Industrial Control PCBA Medical Equipment PCBA

Medical Equipment PCBA PCBA Testing Service

PCBA Testing Service Certification Application

Certification Application RoHS Certification Application

RoHS Certification Application REACH Certification Application

REACH Certification Application CE Certification Application

CE Certification Application FCC Certification Application

FCC Certification Application CQC Certification Application

CQC Certification Application UL Certification Application

UL Certification Application Transformers, Inductors

Transformers, Inductors High Frequency Transformers

High Frequency Transformers Low Frequency Transformers

Low Frequency Transformers High Power Transformers

High Power Transformers Conversion Transformers

Conversion Transformers Sealed Transformers

Sealed Transformers Ring Transformers

Ring Transformers Inductors

Inductors Wires,Cables Customized

Wires,Cables Customized Network Cables

Network Cables Power Cords

Power Cords Antenna Cables

Antenna Cables Coaxial Cables

Coaxial Cables Net Position Indicator

Net Position Indicator Solar AIS net position indicator

Solar AIS net position indicator Capacitors

Capacitors Connectors

Connectors Diodes

Diodes Embedded Processors & Controllers

Embedded Processors & Controllers Digital Signal Processors (DSP/DSC)

Digital Signal Processors (DSP/DSC) Microcontrollers (MCU/MPU/SOC)

Microcontrollers (MCU/MPU/SOC) Programmable Logic Device(CPLD/FPGA)

Programmable Logic Device(CPLD/FPGA) Communication Modules/IoT

Communication Modules/IoT Resistors

Resistors Through Hole Resistors

Through Hole Resistors Resistor Networks, Arrays

Resistor Networks, Arrays Potentiometers,Variable Resistors

Potentiometers,Variable Resistors Aluminum Case,Porcelain Tube Resistance

Aluminum Case,Porcelain Tube Resistance Current Sense Resistors,Shunt Resistors

Current Sense Resistors,Shunt Resistors Switches

Switches Transistors

Transistors Power Modules

Power Modules Isolated Power Modules

Isolated Power Modules DC-AC Module(Inverter)

DC-AC Module(Inverter) RF and Wireless

RF and Wireless