Test Point Design to Meet the Reliability Requirements of Flying Probe Testing

2025-09-25

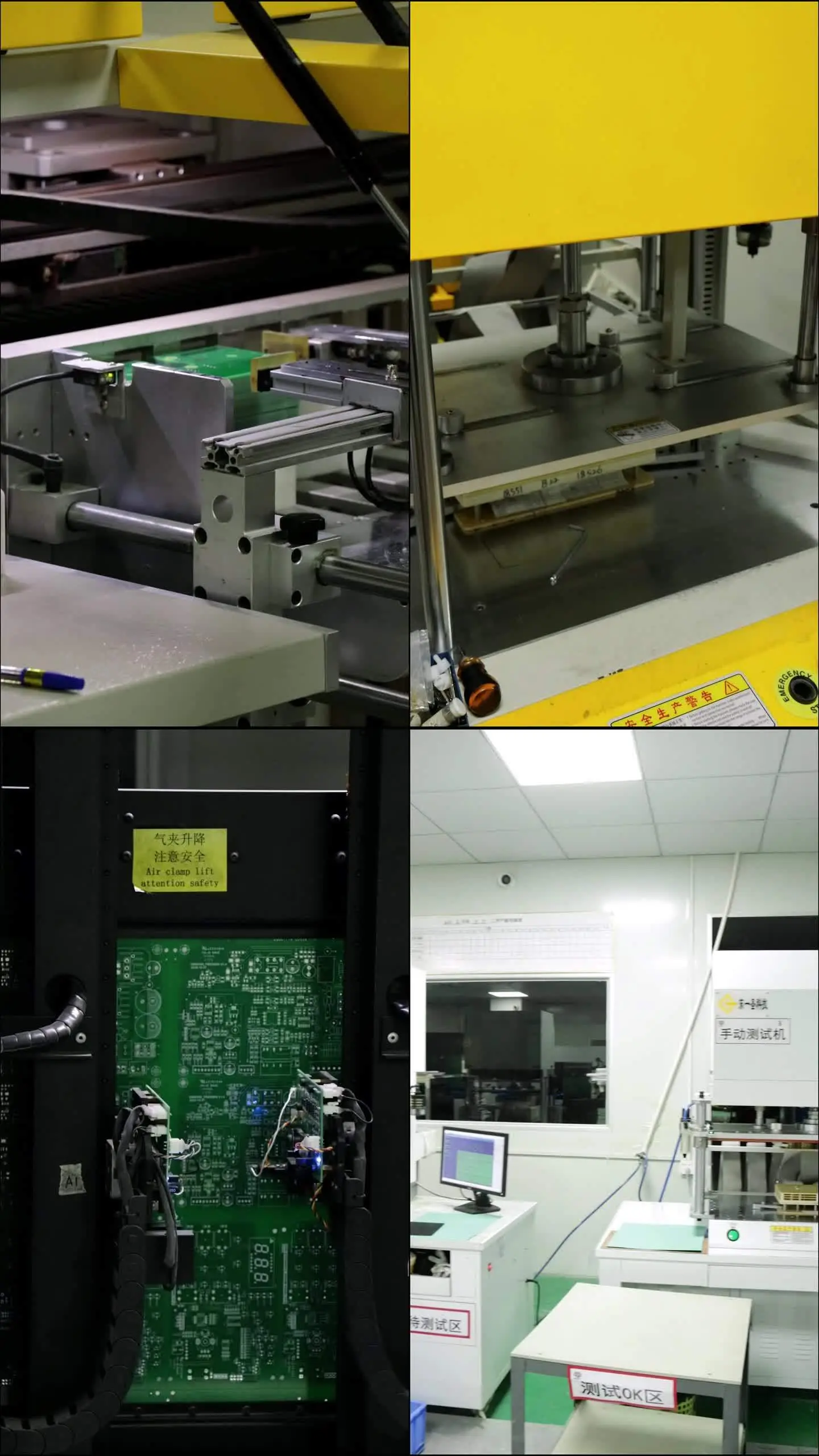

Flying probe testing is a key inspection link in the post-manufacturing stage of PCBs. It uses movable "flying probes" to contact test points on PCBs to detect parameters such as circuit continuity, impedance, and short circuits. It is especially suitable for testing small-batch, high-density PCBs (such as HDI boards and Flexible Pcbs). As the only contact medium between flying probes and circuits, test point design directly determines theaccuracy (test coverage ≥98%), stability (poor contact rate ≤0.1%), and effICiency (test time ≤30 seconds/board) of the test.

If the test point design is unreasonable, problems such as "probe slipping", "excessive contact resistance", and "test point damage" are likely to occur, leading to misjudgment (misjudgment rate >2%) or test interruption, increasing production costs. Therefore, it is necessary to systematically design test points based on the mechanical characteristics (probe pressure, movement accuracy) and electrical characteristics (contact resistance, signal integrity) of flying probe testing.

2. Core Reliability Requirements for Test Points in Flying Probe Testing

The probes of flying probe testing equipment usually have a diameter of 0.1-0.3mm, a movement accuracy of ±0.01mm, and a contact pressure of 50-200g. Based on this, test points must meet the following reliability requirements:

- Mechanical Reliability: Test points must withstand repeated probe contacts (service life ≥1000 contacts) without falling off or deforming; there is no slipping or offset when the probe contacts, and the positioning accuracy is ≤±0.02mm.

- Electrical Reliability: The connection resistance between the test point and the circuit is ≤50mΩ; the contact resistance is stable (fluctuation ≤10mΩ) to avoid continuity misjudgment due to poor contact.

- Process Compatibility: Test point design must be compatible with PCB manufacturing processes (such as solder mask and gold plating) and not affect subsequent assembly (such as component mounting and housing installation).

3. Test Point Design Methods to Meet Flying Probe Testing Reliability

3.1 Size and Shape Design of Test Points

Size and shape directly affect the stability of probe contact and must match the specifications of flying probes:

- Size Design: The recommended diameter of test points is 0.4-0.8mm (for probes with a diameter of 0.15-0.2mm), and the minimum is not less than 0.3mm. A too-small diameter (<0.3mm) easily leads to difficult probe positioning and a poor contact rate >5%; a too-large diameter (>1mm) occupies too much PCB space, which is not conducive to high-density layout.

- The copper foil thickness of test points must be consistent with that of the PCB (usually 1oz=35μm). If thickened copper (2oz=70μm) is used, the suRFace flatness must be ensured to be ≤0.01mm to avoid uneven force when the probe contacts.

Shape Selection: Priority is given to circular test points, which have uniform probe contact area and high positioning accuracy (deviation ≤±0.01mm); square or special-shaped test points should be avoided, as such shapes easily lead to probe edge contact and large contact resistance fluctuation (>20mΩ).

If space is limited, "oval test points" (major axis 0.6mm, minor axis 0.4mm) can be used, but it is necessary to ensure that the probe contact direction is consistent with the major axis to improve contact stability.

3.2 Layout and Spacing Design of Test Points

Reasonable layout and spacing can avoid probe collisions and ensure test efficiency and accuracy:

- Layout Principle: Test points must be laid out in the "accessible area" of the PCB — avoiding blocked areas such as components, connectors, and housing buckles, with a distance of ≥2mm from the board edge and ≥1mm from component pads to prevent the probe from colliding with components during contact (collision probability ≤0.05%).

- High-density PCBs adopt a "grid layout", and the center spacing of test points is designed as an integer multiple of the minimum probe movement step (usually 0.1mm). The recommended spacing is 1.0-2.0mm to ensure smooth movement of flying probes and shorten the test time by 20%-30%.

- Test points for key signals (such as power supply and ground) must be separately laid out at the PCB edge to facilitate priority testing and quickly troubleshoot power supply short-circuit problems.

Spacing Requirements: The center spacing of adjacent test points is ≥0.8mm (for test points with a diameter of 0.4mm), and the minimum is not less than 0.6mm to avoid probe collisions during the movement of flying probes (collision rate ≤0.1%).

The distance between test points and the PCB edge is ≥1.5mm to prevent probe positioning deviation caused by PCB edge deformation during testing.

3.3 Surface Treatment and Connection Design of Test Points

Surface treatment affects contact resistance and durability, and connection design ensures reliable conduction between test points and circuits:

- Surface Treatment Method: Priority is given to electroless gold plating (gold layer thickness 0.8-1.2μm), which has stable contact resistance (≤30mΩ) and good wear resistance (service life ≥1000 contacts); tin plating (tin layer thickness 5-10μm) can be used secondarily, but attention must be paid to the tin whisker problem, which can be improved by hot air solder leveling (HASL) to improve surface flatness.

- OSP (organic solderability preservative) should be avoided for test point treatment, as the OSP layer is easy to wear and has large contact resistance fluctuation (>50mΩ), resulting in low test reliability.

Connection Design: Test points must be connected to the tested network through "independent wires" with a wire width ≥0.2mm. Sharing with other wires is avoided to prevent test misjudgment caused by signal crosstalk.

For multi-layer PCBs, test points must be connected to the inner layer network through vias with a via diameter ≥0.2mm and concentric with the test point (deviation ≤0.02mm) to ensure conduction resistance ≤50mΩ.

3.4 Solder Mask and Marking Design of Test Points

Solder mask and marking design can improve the recognizability and protection of test points:

- Solder Mask Design: The surface of test points needs to be "opened to expose copper", and the solder mask opening diameter is 0.2-0.3mm larger than the test point diameter (e.g., test point diameter 0.5mm, opening diameter 0.7-0.8mm) to ensure that the probe can accurately contact the test point and avoid poor contact caused by solder mask coverage.

- The edge of the solder mask opening must be smooth and burr-free, with a concentricity deviation of ≤0.05mm from the test point to prevent the probe from being scratched by the edge of the solder mask during contact.

Marking Design: Silk screen marks (such as "TP1", "TP2") are added near the test points with a font size ≥0.8mm to facilitate test engineers to check the test point positions and reduce human operation errors (error rate ≤0.1%).

For symmetrically laid out PCBs, direction marks (such as "TP1-A", "TP1-B") must be added to the test point marks to avoid direction confusion during flying probe testing.

3.5 Optimized Test Point Design in Special Scenarios

Differentiated designs are required for special PCBs such as high-density, flexible, and high-frequency PCBs:

- High-Density PCBs (Line Width/Spacing ≤0.1mm): "Miniature test points" (diameter 0.3-0.4mm) are used with thin-diameter probes (0.1mm); at the same time, a "staggered layout" is adopted to avoid probe collisions caused by dense arrangement of test points.

- Test points can be laid out at the bottom of components (must match the component package, e.g., a 0.3mm test point can be placed at the bottom of a 0402 package), and contact testing is realized using the Z-axis movement accuracy (±0.005mm) of flying probes.

Flexible PCBs (FPC): Test points must be designed in the "rigid area" of FPC (such as the reinforcement plate position) to avoid probe positioning deviation caused by FPC deformation during testing.

"Gold-plated test pads" (diameter 0.5mm, thickness 1.0μm) are used to improve the wear resistance of test points and adapt to the bending characteristics of FPC.

High-Frequency PCBs (Signal Rate ≥25Gbps): Test points must match the characteristic impedance of the transmission line (e.g., 50Ω), which can be achieved by adjusting the test point diameter and wire width (e.g., 0.5mm test point corresponds to 0.3mm wire) to avoid signal reflection caused by impedance mutation (return loss ≥-15dB).

The spacing between test points must be ≥2 times the signal wavelength (e.g., 25Gbps signal wavelength ≈60mm, spacing ≥120mm) to reduce electromagnetic coupling between test points.

4. Verification Methods for Test Point Reliability

The reliability of test point design is verified through the following tests:

- Contact Stability Test: Use flying probe testing equipment to perform 1000 contact tests on the same test point, record the contact resistance value. The contact resistance is required to be ≤50mΩ, the fluctuation is ≤10mΩ, and there is no contact failure.

- Mechanical Durability Test: After repeatedly contacting the test point 1000 times with a probe (pressure 150g), observe the test point surface through a microscope (magnification 50x). No falling off, deformation, or plating wear (wear area ≤5%) is required.

- Electrical Performance Test: For test points of high-frequency PCBs, use a vector network analyzer to test S-parameters. Within the signal working frequency band, the insertion loss is required to be ≤0.5dB, and the return loss is ≥-18dB.

5. Common Problems and Solutions

| Common Problems | Causes | Solutions |

|---|---|---|

| Poor Test Point Contact | Too small solder mask opening; too small test point diameter; OSP surface treatment | Increase the solder mask opening to test point diameter +0.3mm; increase the test point diameter to 0.5mm; switch to electroless gold plating surface treatment |

| Probe Collides with Test Points | Too small test point spacing; dense layout | Increase the test point spacing to 1.0mm; adopt staggered layout or grid layout |

| High-Frequency Signal Test Misjudgment | Test point impedance mismatch; coupling between test points | Optimize test point and wire size to match impedance; increase test point spacing to ≥2λ |

PCB

PCB FPC

FPC Rigid-Flex

Rigid-Flex FR-4

FR-4 HDI PCB

HDI PCB Rogers High-Frequency Board

Rogers High-Frequency Board PTFE Teflon High-Frequency Board

PTFE Teflon High-Frequency Board Aluminum

Aluminum Copper Core

Copper Core PCB Assembly

PCB Assembly LED light PCBA

LED light PCBA Memory PCBA

Memory PCBA Power Supply PCBA

Power Supply PCBA New Energey PCBA

New Energey PCBA Communication PCBA

Communication PCBA Industrial Control PCBA

Industrial Control PCBA Medical Equipment PCBA

Medical Equipment PCBA PCBA Testing Service

PCBA Testing Service Certification Application

Certification Application RoHS Certification Application

RoHS Certification Application REACH Certification Application

REACH Certification Application CE Certification Application

CE Certification Application FCC Certification Application

FCC Certification Application CQC Certification Application

CQC Certification Application UL Certification Application

UL Certification Application Transformers, Inductors

Transformers, Inductors High Frequency Transformers

High Frequency Transformers Low Frequency Transformers

Low Frequency Transformers High Power Transformers

High Power Transformers Conversion Transformers

Conversion Transformers Sealed Transformers

Sealed Transformers Ring Transformers

Ring Transformers Inductors

Inductors Wires,Cables Customized

Wires,Cables Customized Network Cables

Network Cables Power Cords

Power Cords Antenna Cables

Antenna Cables Coaxial Cables

Coaxial Cables Net Position Indicator

Net Position Indicator Solar AIS net position indicator

Solar AIS net position indicator Capacitors

Capacitors Connectors

Connectors Diodes

Diodes Embedded Processors & Controllers

Embedded Processors & Controllers Digital Signal Processors (DSP/DSC)

Digital Signal Processors (DSP/DSC) Microcontrollers (MCU/MPU/SOC)

Microcontrollers (MCU/MPU/SOC) Programmable Logic Device(CPLD/FPGA)

Programmable Logic Device(CPLD/FPGA) Communication Modules/IoT

Communication Modules/IoT Resistors

Resistors Through Hole Resistors

Through Hole Resistors Resistor Networks, Arrays

Resistor Networks, Arrays Potentiometers,Variable Resistors

Potentiometers,Variable Resistors Aluminum Case,Porcelain Tube Resistance

Aluminum Case,Porcelain Tube Resistance Current Sense Resistors,Shunt Resistors

Current Sense Resistors,Shunt Resistors Switches

Switches Transistors

Transistors Power Modules

Power Modules Isolated Power Modules

Isolated Power Modules DC-AC Module(Inverter)

DC-AC Module(Inverter) RF and Wireless

RF and Wireless