Controlling Bump Coplanarity <5μm in Flip Chip Assembly

2025-06-30

1. Coplanarity Definition & Impact

-

Coplanarity:

Max-Min bump height variation ≤5μm -

Failure Risks:

Deviation Effect 5~10μm Voiding >15% >10μm Die cracking (↑300% thermal stress)

2. Bump FabrICation Control

2.1 Electroplating Optimization

| Parameter | Standard | Coplanarity Impact |

|---|---|---|

| Plating flow uniformity | Velocity delta <5% | ±1.2μm |

| Current density | 1.5±0.2 ASD | ±0.8μm |

| PR thickness uniformity | ≤±1.5% (200μm) | ±0.5μm |

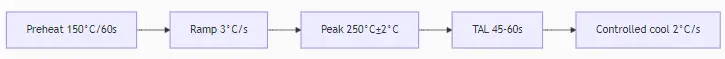

2.2 Reflow Sphering

-

Profile:

-

Atmosphere:

N₂+H₂ mix (O₂<20ppm, dew point<-40°C)

3. Wafer-Level Correction

| Technique | Accuracy | Correction Method |

|---|---|---|

| White light inteRFerometer | 0.1μm | Electroplating parameter adjustment |

| 3D laser confocal | 0.15μm | Local laser reflow (5J/cm²) |

| Flying probe | 1μm | Mark for downstream compensation |

4. Substrate Surface Treatment

4.1 Pad Coplanarity Control

| Process | Key Technique | Effect |

|---|---|---|

| ENIG | Thickness CV≤3% | Flatness ±0.8μm |

| Laser drilling filling | Dimple<2μm | ↓40% bump delta |

| mSAP | Cu thickness tolerance ±1.5μm | Pad delta<1μm |

4.2 Flux Coating

-

Nano-spray:

-

Thickness uniformity ±5% (target 15μm)

-

Viscosity: 120±10 mPa·s @25°C

-

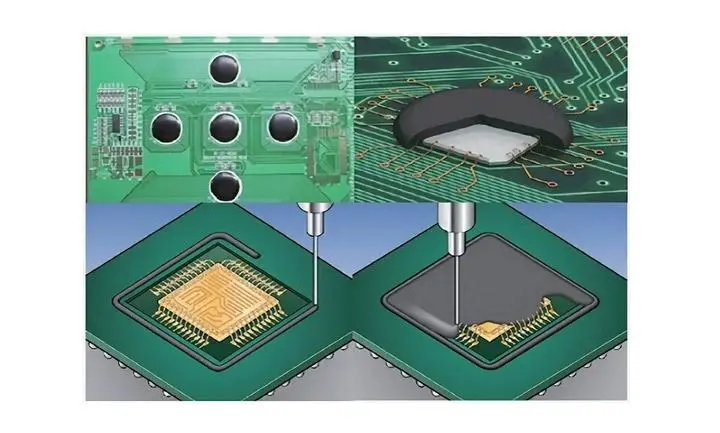

5. Critical Placement Parameters

| Parameter | Target | Tolerance | Sensitivity |

|---|---|---|---|

| Placement force | 5N/chip | ±0.2N | 0.3μm/N |

| Thermo-compression temp | 150°C | ±2°C | 0.1μm/°C |

| Tilt compensation | Auto-cal (0.001°) | 0.05μm/mrad | - |

| Nozzle flatness | ≤1μm | 0.05μm | Direct add-on |

6. Reflow Coplanarity Maintenance

6.1 Thermal Uniformity

| Solution | Implementation | ΔT Substrate |

|---|---|---|

| Zoned heating | 12-zone PID control | ≤±1.5°C |

| Bottom N₂ jet | 5m/s flow, turbulence<5% | ↓60% warpage |

| Thermal buffer | Graphene sheet (λ=1500W/mK) | Gradient ↓70% |

6.2 Warpage Control Structures

-

Substrate Design:

-

Symmetric routing (Cu balance ±5%)

-

Dummy bumps (↑30% edge density)

-

-

Fixture Optimization:

-

Ceramic pressure plate (CTE=7ppm/°C)

-

Micro-spring array (0.05MPa±5%)

-

7. Inspection & SPC

7.1 In-line Metrology

| Technology | Accuracy | Speed |

|---|---|---|

| Moiré projection | 0.5μm | 0.5s/chip |

| X-ray CT | 1μm | 3min/chip |

7.2 SPC Rules

-

Chart Type: Xbar-R (subgroup=5)

-

Out-of-control:

-

Point beyond UCL/LCL (UCL=4.2μm, LCL=0)

-

7 consecutive points on one side

-

-

CPK Target: ≥1.67 (PPM<0.54)

8. Failure Analysis

| Failure Mode | Root Cause | Corrective Action |

|---|---|---|

| Local bump collapse | Non-uniform flux | Ultrasonic atomization (40kHz) |

| Edge bump lifting | Substrate CTE anisotropy | Pre-bake (125°C×2h) |

| Post-TC coplanarity loss | Nozzle flatness OOS | Daily calibration + piezo compensation |

PCB

PCB FPC

FPC Rigid-Flex

Rigid-Flex FR-4

FR-4 HDI PCB

HDI PCB Rogers High-Frequency Board

Rogers High-Frequency Board PTFE Teflon High-Frequency Board

PTFE Teflon High-Frequency Board Aluminum

Aluminum Copper Core

Copper Core PCB Assembly

PCB Assembly LED light PCBA

LED light PCBA Memory PCBA

Memory PCBA Power Supply PCBA

Power Supply PCBA New Energey PCBA

New Energey PCBA Communication PCBA

Communication PCBA Industrial Control PCBA

Industrial Control PCBA Medical Equipment PCBA

Medical Equipment PCBA PCBA Testing Service

PCBA Testing Service Certification Application

Certification Application RoHS Certification Application

RoHS Certification Application REACH Certification Application

REACH Certification Application CE Certification Application

CE Certification Application FCC Certification Application

FCC Certification Application CQC Certification Application

CQC Certification Application UL Certification Application

UL Certification Application Transformers, Inductors

Transformers, Inductors High Frequency Transformers

High Frequency Transformers Low Frequency Transformers

Low Frequency Transformers High Power Transformers

High Power Transformers Conversion Transformers

Conversion Transformers Sealed Transformers

Sealed Transformers Ring Transformers

Ring Transformers Inductors

Inductors Wires,Cables Customized

Wires,Cables Customized Network Cables

Network Cables Power Cords

Power Cords Antenna Cables

Antenna Cables Coaxial Cables

Coaxial Cables Net Position Indicator

Net Position Indicator Solar AIS net position indicator

Solar AIS net position indicator Capacitors

Capacitors Connectors

Connectors Diodes

Diodes Embedded Processors & Controllers

Embedded Processors & Controllers Digital Signal Processors (DSP/DSC)

Digital Signal Processors (DSP/DSC) Microcontrollers (MCU/MPU/SOC)

Microcontrollers (MCU/MPU/SOC) Programmable Logic Device(CPLD/FPGA)

Programmable Logic Device(CPLD/FPGA) Communication Modules/IoT

Communication Modules/IoT Resistors

Resistors Through Hole Resistors

Through Hole Resistors Resistor Networks, Arrays

Resistor Networks, Arrays Potentiometers,Variable Resistors

Potentiometers,Variable Resistors Aluminum Case,Porcelain Tube Resistance

Aluminum Case,Porcelain Tube Resistance Current Sense Resistors,Shunt Resistors

Current Sense Resistors,Shunt Resistors Switches

Switches Transistors

Transistors Power Modules

Power Modules Isolated Power Modules

Isolated Power Modules DC-AC Module(Inverter)

DC-AC Module(Inverter) RF and Wireless

RF and Wireless